开关电源设计中,我们常常使用到一个电阻串联一个电容构成的RC电路, RC电路性能会直接影响到产品性能和稳定性。本文将为大家介绍一种既能降低开关管损耗,且可降低变压器的漏感和尖峰电压的RC电路。

高频开关电源在开关管关断时,电压和电流的重叠引起的损耗是开关电源损耗的主要部分,同时,由于电路中存在寄生电感和寄生电容,在功率开关管关断时,电路中也会出现过电压并且产生振荡。如果尖峰电压过高,就会损坏开关管。同时,振荡的存在也会使输出纹波增大。为了降低关断损耗和尖峰电压,需要在开关管两端并联RC缓冲电路以改善电路的性能。

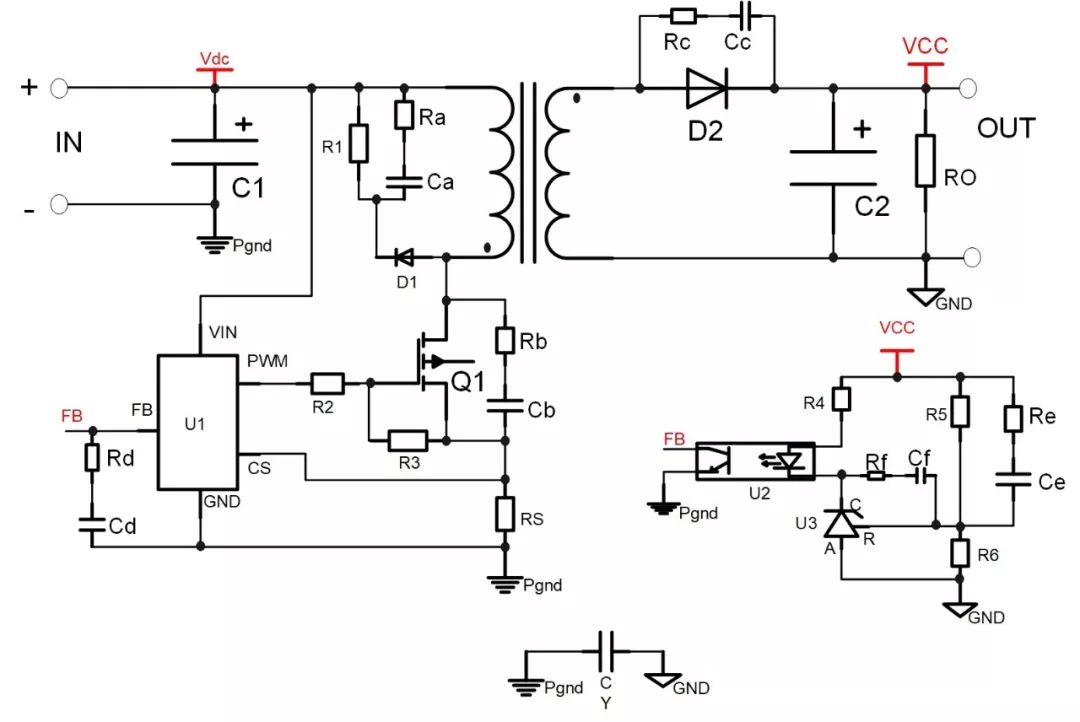

图1

图1所示的是一个简单的反激式开关电源电路,从图中可以看出RC电路在图中的出现过6次从RaCa—RfCf,每个RC电路的位置不同,作用也不一样。本文介绍的是图1中RbCb,RcCc构成的RC吸收电路。这两个RC电路在图中主要作用是:

减少导通或关断损耗;

降低电压或电流尖峰;

可以间接的改善EMI特性。

在设计RC吸收电路时,我们必须了解整个电源网络的几个重要参数,比如输入电压、输入电流、尖峰电压、尖峰电流等。在图1所示当Q1关断时,源极电压开始上升到2Vdc,而电容Cb限制了源极(D)电压的上升速度,同时减小了上升电压和下降电流的重叠,从而减低了开关管Q1的损耗。而在下次开关关断之前,Cb必须将已经充满的电压放完,放电路径为Cb、Rb、Q1。

图2 开关管源极(D)的Vds电压波形

图2-A表示的是开关管Q1没有加RC吸收电路的Vds电压波形,图中明显的看出,当开关管Q1断开时,Vds电压迅速上升至最高点,而后伴随这震荡下跌,震荡频率为20MHZ。

图2-B表示的是开关管上加了RC吸收电路的Vds电压波形,相对与图2-A,在加了RC吸收电路后,开关管断开瞬间,Vds电压上升比较平缓,且在上升到最高电压跌落时不会产生高频震荡,EMI特性也会偏好。

在感性负载中,开关器件关断的瞬间,如果此时感性负载的磁通不为零,根据愣次定律便会产生一个自感电动势,对外界辞放磁场储能,为简单起见,一般都采用RC吸收回路,将这部份能量以热能的方式消耗掉。

设计RC吸收回路参数,需要先确定磁场储能的大小,在反激变压器中,磁场储能由两部份辞放,其中大部份是通过互感向二次侧提供能量,只有漏感部份要通过RC回路处理,需要测量励磁电感,互感及漏感值,再求得RC回路的初始电流值。

R的取值,以开关所能承受的瞬时反压,比初始电流值;此值过小则动态功耗过大,引值过大则达不到保护开关的作用;

C的取值,则需要满足在钳位电平下能够储存磁能的一半,且满足一定的dV/dt,C关断缓冲,R开通限流,电阻的阻值基本可以按照:

R=(sqrt(Llk/Cj))/n 这个公式计算,功率根据实际情况选择,C一般都在102——103之间选择,选C时在考虑吸收效果的同时还需考虑EMI的相位和后面输出电容的纹波电流应力,则有:

C=(Ip*Tf)/(2*2*Vdc)

Ip:峰值电流

Tf:集电极电流从初始值下降到零的时间

Vdc:输入的直流电压

R=Ton(min)/(3C)

Ton(min):开关管最小的导通时间

总结

根据以上给出的公式,可以很方便地选择出合适的RC吸收电路。但在设计时,应该根据整个电源设计的性能指标,通过实际调试才能得到真正合适的参数。有时候,为了达到系统的性能指标,牺牲一定的效率也是必要的。总之,在设计RC吸收电路参数时,必须综合考虑性能和效率,最终选择合适的RC参数。

ZLG致远电子自主研发、生产的隔离电源模块已有近20年的行业积累,目前产品具有宽输入电压范围,隔离1000VDC、1500VDC、3000VDC及6000VDC等多个系列,封装形式多样,兼容国际标准的SIP、DIP等封装。

同时,ZLG致远电子为保证电源产品性能建设了行业内一流的测试实验室,配备最先进、齐全的测试设备,全系列隔离DC-DC电源通过完整的EMC测试,静电抗扰度高达4KV、浪涌抗扰度高达2KV,可应用于绝大部分复杂恶劣的工业现场,为用户提供稳定、可靠的电源隔离解决方案。